Introduction

Tone control up_down drive is a feature often found on modern guitar amplifiers, allowing players to easily adjust their tone left or right. Not only does it allow the player to find the exact sound they’re looking for and make minute adjustments to suit their tastes, but it also benefits those using multiple amps at once and needing variation between them. The tone control is a great addition to an amp, as it allows versatility in overall sound without adding unnecessary complexity to the set – up.

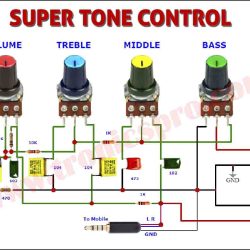

Circuit Diagram

of Tone Control Up_Down Drive

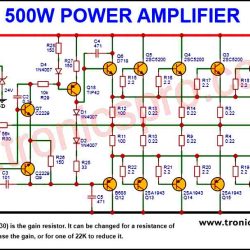

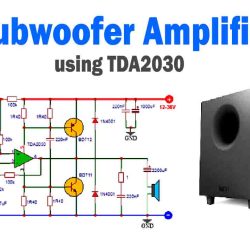

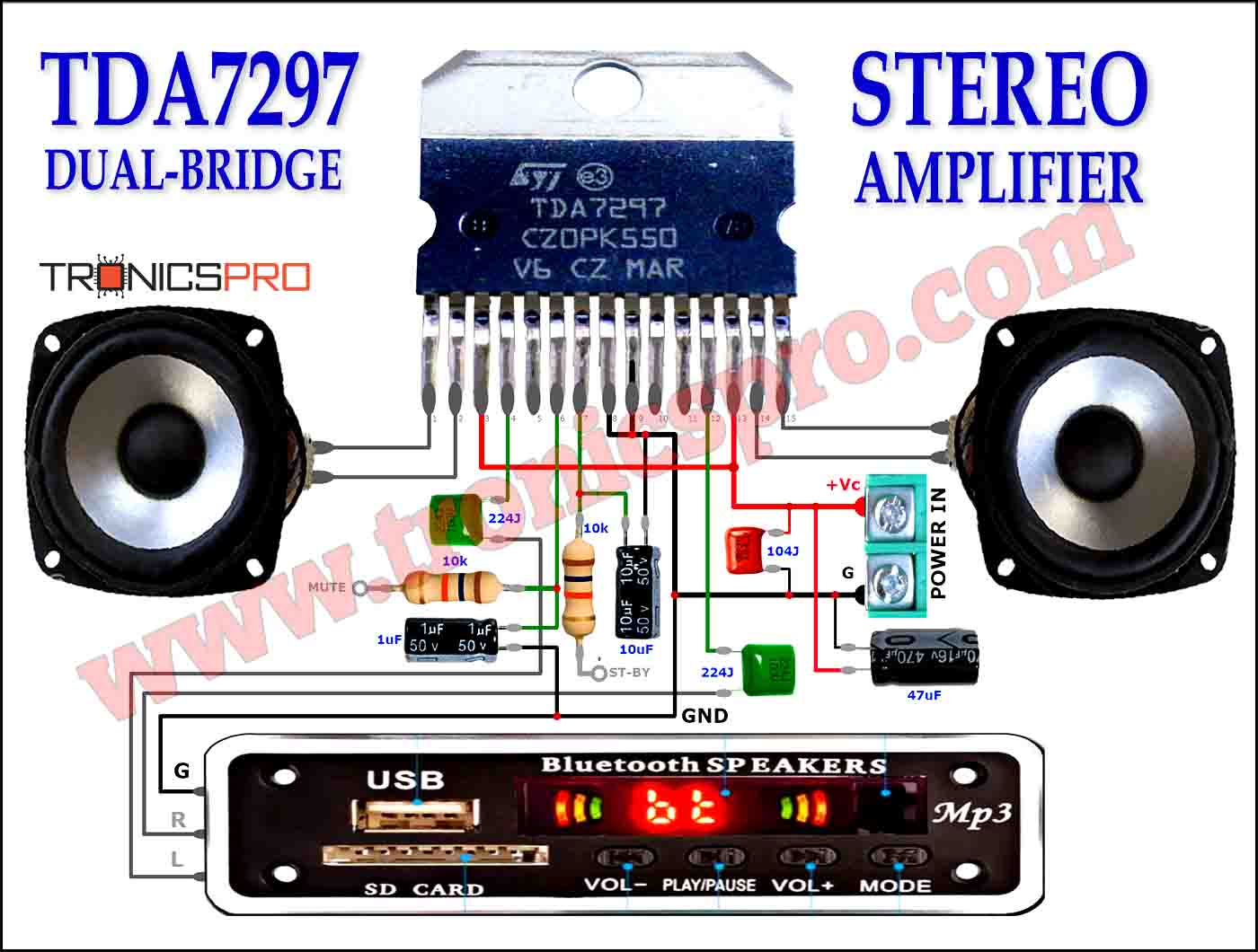

More Circuit Layouts

Working Explanation

of Tone Control Up_Down Drive

The tone controls use electronic switches that are operated by a multi-position selector. The present circuit is intended as a replacement for this selector and has facilities for operating the tone controls via an up key and a down key. A third key enables the user to switch over rapidly to a preprogrammed position of the relevant tone control.

The electronic switches are driven by a BCD-to-decimal decoder Type 4028 (IC3), which in turn is controlled by a 4-bit preset up/down counter (IC2). The counter uses the three lowest bits only. The MSB of decoder IC3 is permanently low. Only the eight lowest outputs of the decoder are used and these are linked via Kâ‚ to the control inputs of ICâ‚ and IC2 in the tone controls.

The circuit is operated with S1‚ and S2. Switch S3 is the earlier mentioned preset key. The data for the preset inputs are set with DIP switch S4. Capacitor C3 ensures that when the supply voltage is switched on, the preset data are automatically adopted by the counter.

Each of switches Sâ‚ and S2 drives an S/R bistable (US: flip-flop), which determines the level at the U/D input of counter IC2.

Networks R3-C1‚ and R4-C2, in conjunction with Schmitt, trigger IC1b to provide debouncing and delay the clock pulse slightly. This delay guarantees that the clock pulse (output of IC16) arrives after the state of the counter has been defined.

To prevent the counter jumping from minimum to maximum or vice versa, the clock pulse is disabled in the outermost positions. In the minimum state, this is achieved simply by the carry-out terminal (pin 7) of the counter. In the maximum state, an auxiliary network, consisting of R6, D3, D4, D5/IC1a, and D1, is used.

Diode D2 ensures that when the minim state is reached, pin 5 of IC1‚remains low until S1‚ is pressed. Diode D1‚ does the same in regards to pin 6 of the IC when the maximum state is reached. Resistor R6 serves to reset the clock, which is disabled during down counting; when the down key is pressed, the output of IC1a goes high again.

If an indication is desired of the actual state of the up/down drive, eight high-efficiency LEDs may be added at the output of IC3 (anodes to the output cathodes via a common 10k resistor to ground).

Whether the circuit amplifies or attenuates is indicated by an additional LED at the output of IC1c or IC1d.

During quiescent operation, the circuit draws a current of 20 uA, which rises to about 140 uA when S1‚ or S2 is pressed. Network R7-C7 provides decoupling of the digital circuit from the analog supply.